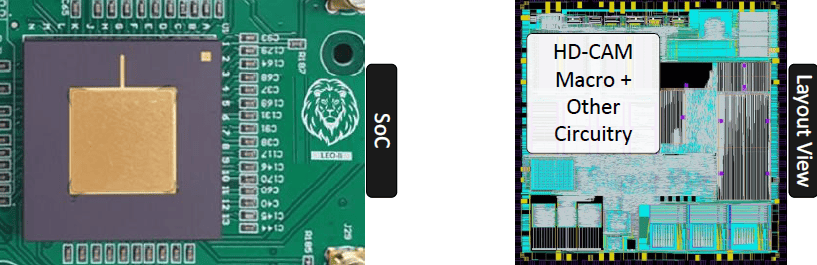

Research Tapeouts (Fabricated Test Chips & Prototypes)

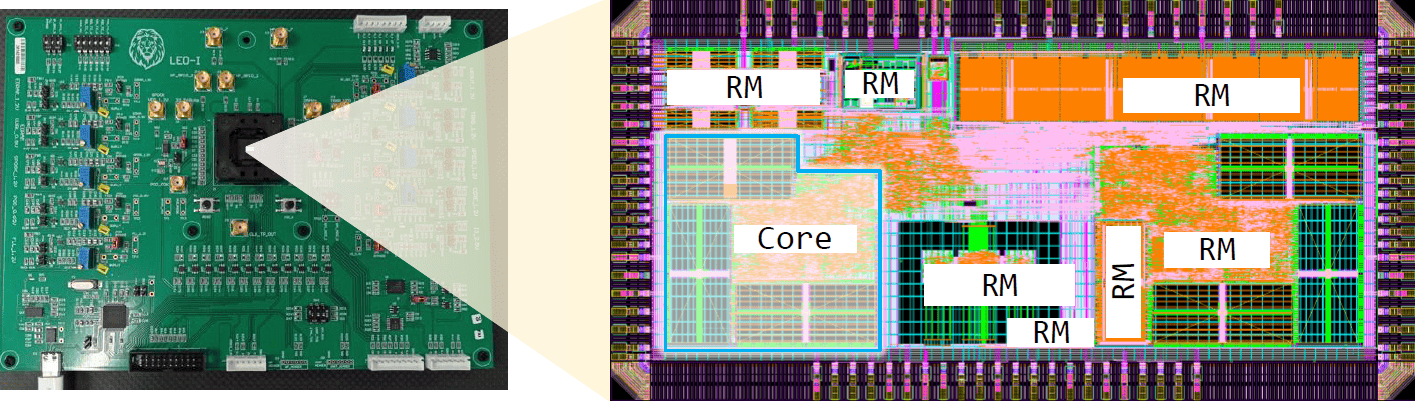

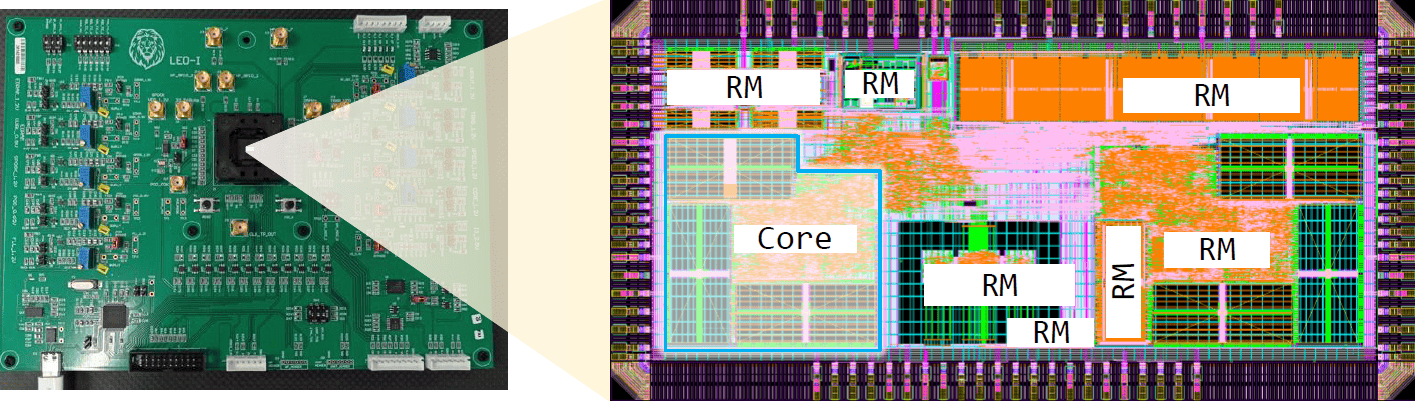

RISC-V-based Research Platform in 65nm

- Joint design with Emerging Nanoscaled Circuits and Systems (EnICS) Laboratories, Bar-Ilan University, Israel

- Chip Name: LEO-I

- Technology: TSMC 65nm

- Role: Backend designer (entire SoC integration)

-

Description: A novel platform for bringing a project from the concept to the tapeout stage in a short

amount of time. An open-source and extendable RISC-V architecture is exploited to build a small area

footprint core. This leads the research platform to be flexible in terms of design integration, while also

allowing fast design cycles of research chips.

Note that, from the SoC layout picture at the top, the research modules (RM) labels over some layout areas correspond to different analog/digital designs from different research groups.

-

Main related publication/s as main author or co-author:

- E. Garzón, R. Golman, O. Harel, T. Noy, Y. Kra, A. Pollock, S. Yuzhaninov, Y. Shoshan, Y. Rudin, Y. Weitzman, et al., "A RISC-V-based research platform for rapid design cycle", IEEE International Symposium on Circuits and Systems (ISCAS), Austin Texas, USA, 28 May-01 Jun., 2022. (link)

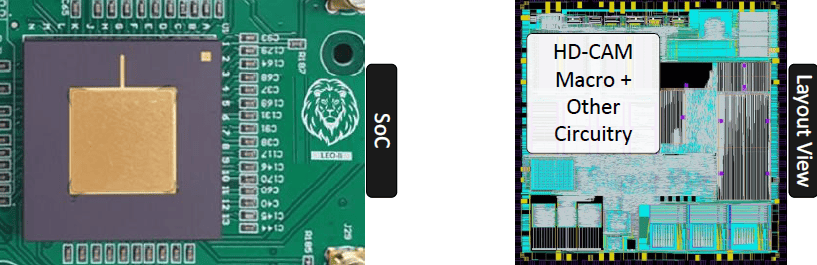

HD-CAM Memory Macro in 65nm

- Full design at Emerging Nanoscaled Circuits and Systems (EnICS) Laboratories, Bar-Ilan University, Israel

- Chip Name: LEO-II

- Technology: TSMC 65nm

- Macro Name: HD-CAM

- Role: Theoretical functional verification by means of simulations, and support in the design and experimental measurements of the memory Macro

-

Description: A novel Hamming distance tolerant CAM (HD-CAM) for energy-efficient in-memory approximate matching applications. The fabricated HD-CAM macro presents high F1-score and AOC values during approximate match operations.

-

Main related publication/s as main author or co-author:

- E. Garzón, E. Rechef, R. Golman, O. Harel, Y. Harary, P. Snapir, M. Lanuzza, A. Teman, L. Yavits, "A 128-kbit Approximate Search-Capable Content-Addressable Memory (CAM) With Tunable Hamming Distance", IEEE Journal of Solid-State Circuits, 2025. (link)

- Y. Harary, P. Snapir, S. Siman Tov, C. Kruphman, E. Rechef, Z. Jahshan, E. Garzón, L. Yavits, "GCOC: A Genome Classifier-On-Chip based on Similarity Search Content Addressable Memory", IEEE Transactions on Biomedical Circuits and Systems, 2024. (link)

- E. Garzón, R. Golman, M. Lanuzza, A. Teman, L. Yavits, "A Low-Complexity Sensing Scheme for Approximate Matching Content-Addressable Memory", IEEE Transactions on Circuits and Systems II, 2023. (link)

- E. Garzón, R. Golman, Z. Jahshan, R. Hanhan, N. Vinshtok-Melnik, M. Lanuzza, A. Teman, L. Yavits, "Hamming Distance Tolerant Content-Addressable Memory (HD-CAM) for DNA Classification", IEEE Access, 2022. (link)

- Y. Harary, P. Snapir, E. Rechef, E. Garzón, L. Yavits, "OCCAM: An Error Oblivious CAM", IEEE Solid-State Circuits Letters, 2024. (link)

Fully-Integrated Temperature Sensor in 180nm

- Full design at Department of Computer Engineering, Modeling, Electronics and Systems, University of Calabria, Rende, Italy

- Technology: TSMC 180nm

- Role: Support in layout design and experimental measurements of the test chip. Design led by Dr. Benjamin Zambrano

-

Description: Fully-integrated, ultralow-power, ring oscillator-based CMOS temperature sensor for energy-constrained, low-cost applications (e.g., Internet-of-Things).

-

Main related publication/s as main author or co-author:

- B. Zambrano, E. Garzón, S. Strangio, F. Crupi, M. Lanuzza, "A 0.05 mm2, 350 mV, 14 nW Fully-Integrated Temperature Sensor in 180-nm CMOS", IEEE Transactions on Circuits and Systems II, 2022. (link)